#### **DIGITAL SYSTEMS: Course Objectives and Lecture Plan**

**Aim**: At the end of the course the student will be able to analyze, design, and evaluate digital circuits, of medium complexity, that are based on SSIs, MSIs, and programmable logic devices.

#### Module 1: Number Systems and Codes (3)

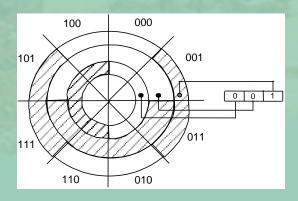

Number systems: Binary, octal, and hexa-decimal number systems, binary arithmetic. Codes: Binary code, excess-3 code, gray code, and error detection and correction codes.

#### Module 2: Boolean Algebra and Logic Functions (5)

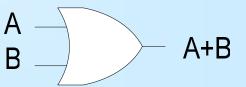

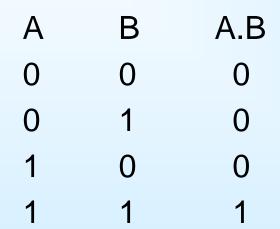

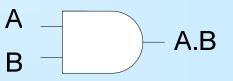

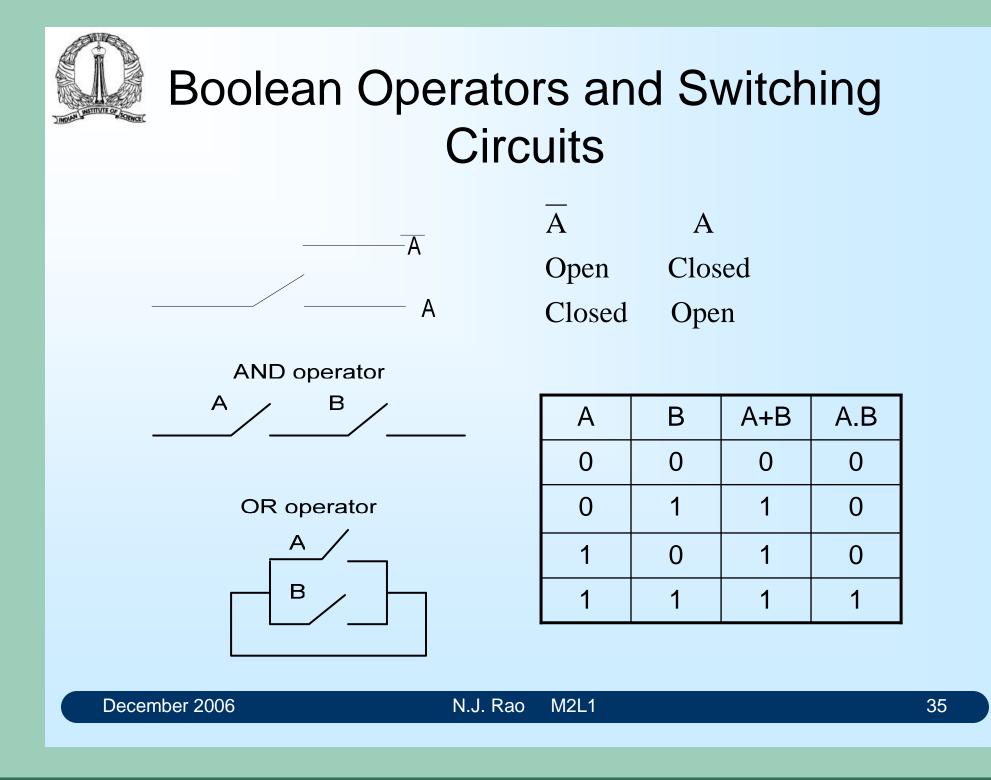

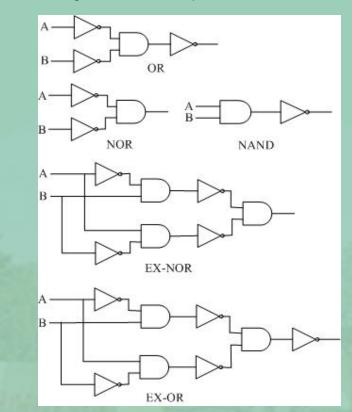

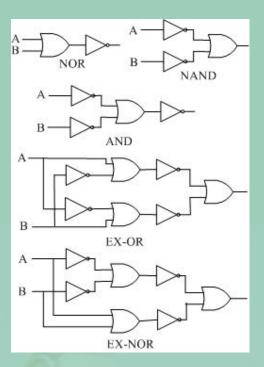

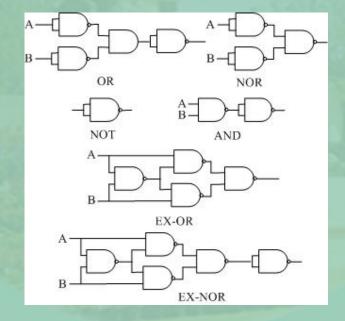

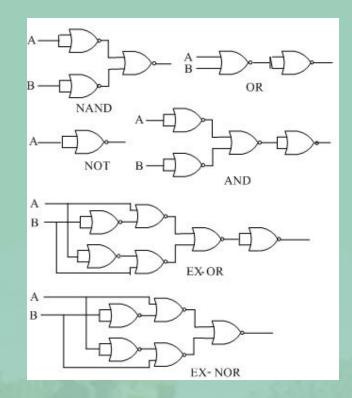

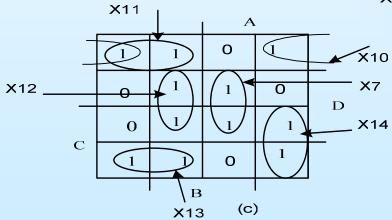

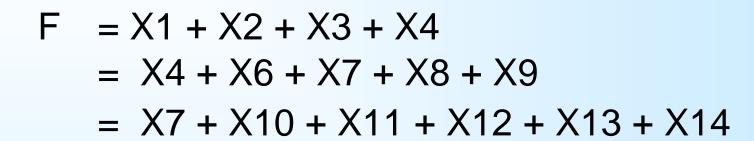

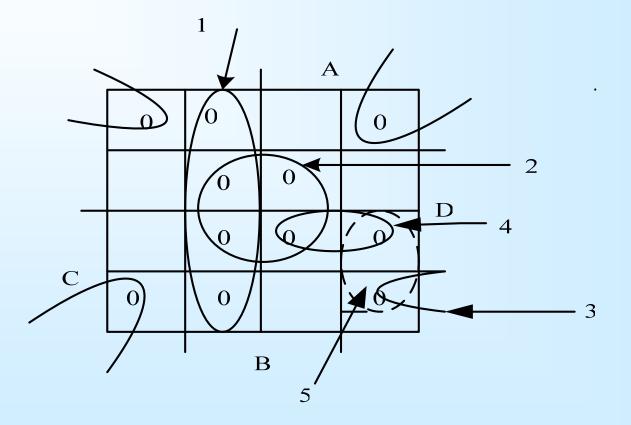

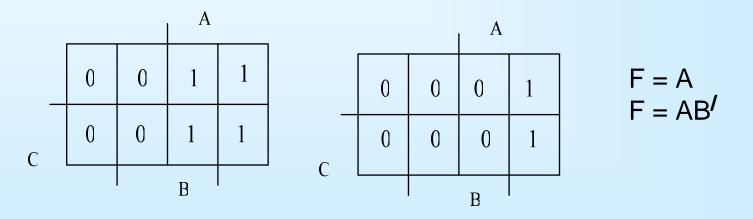

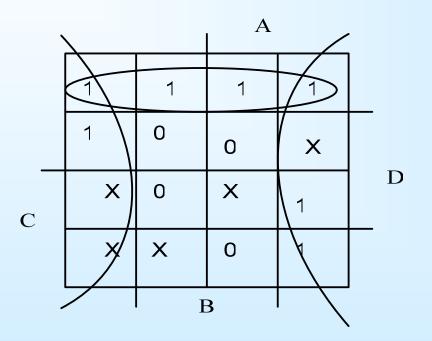

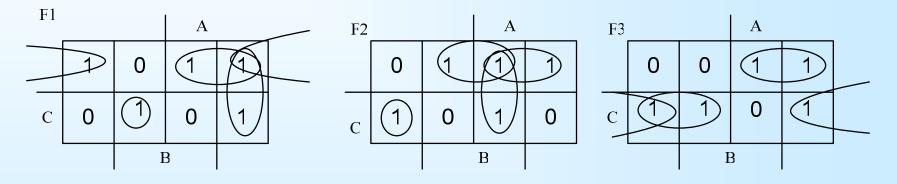

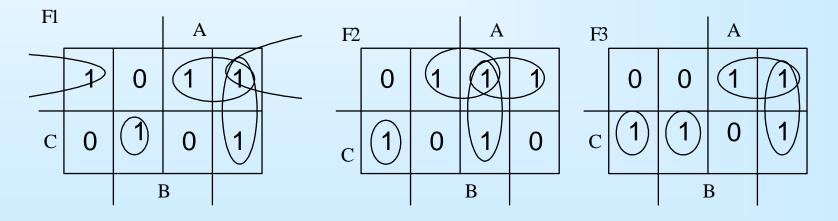

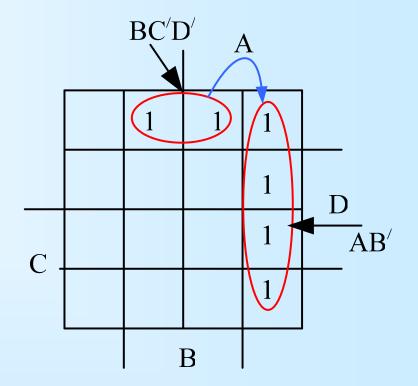

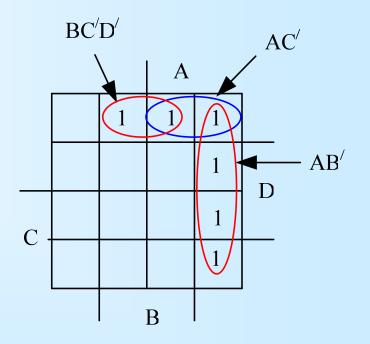

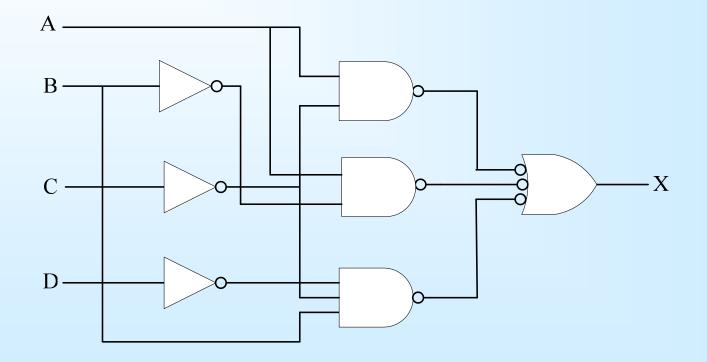

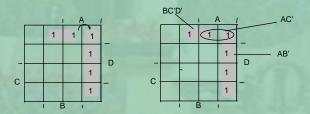

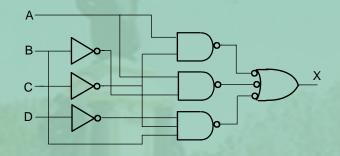

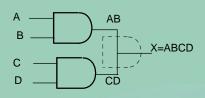

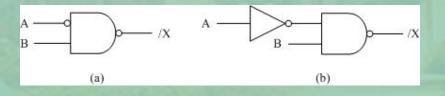

Boolean algebra: Postulates and theorems. Logic functions, minimization of Boolean functions using algebraic, Karnaugh map and Quine – McClausky methods. Realization using logic gates

#### Module 3: Logic Families (4)

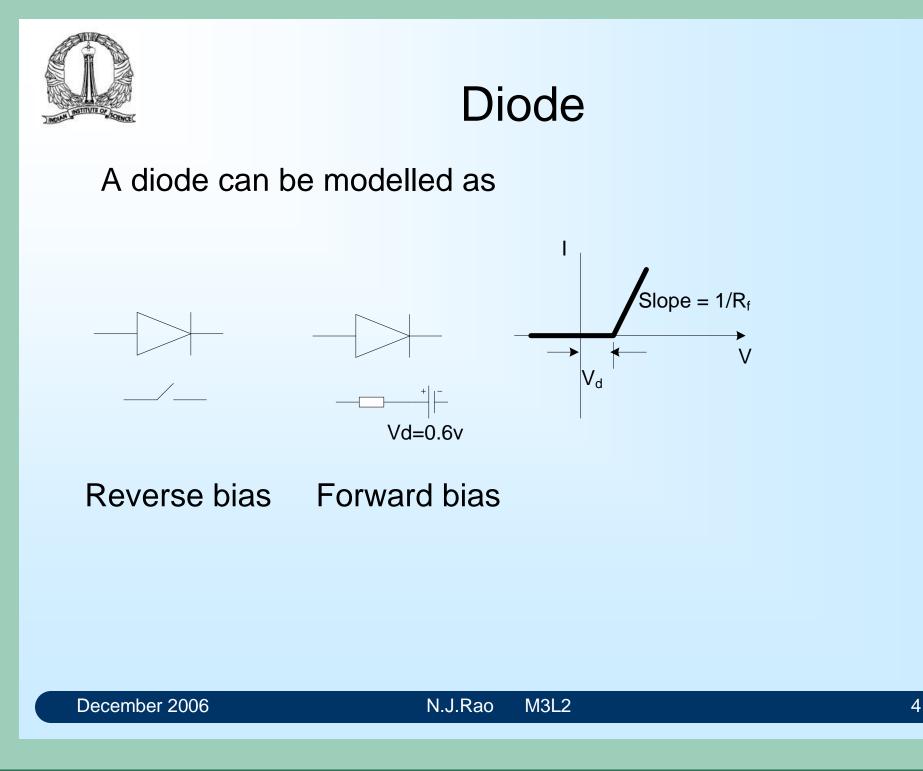

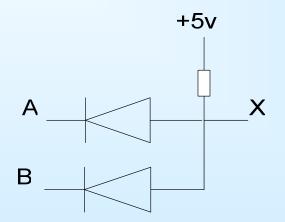

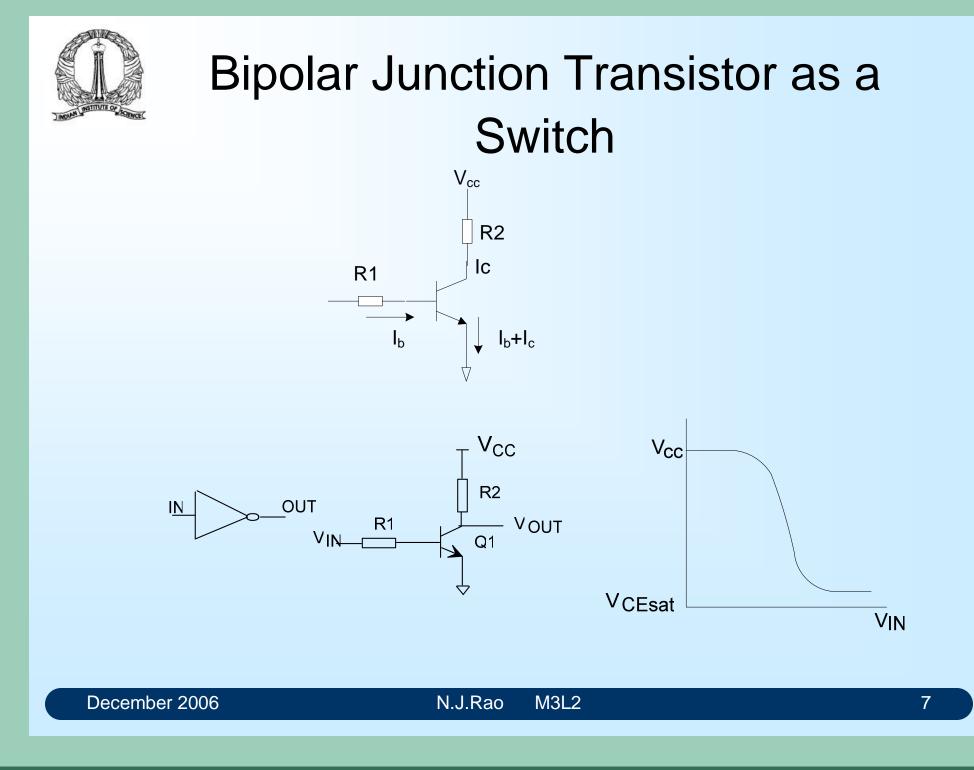

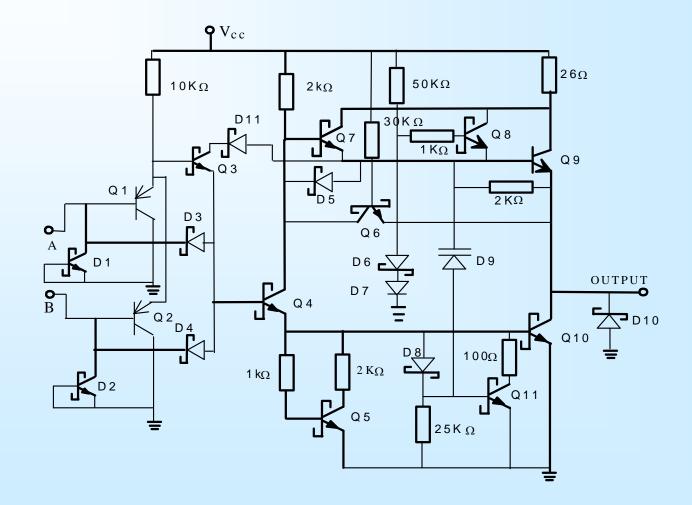

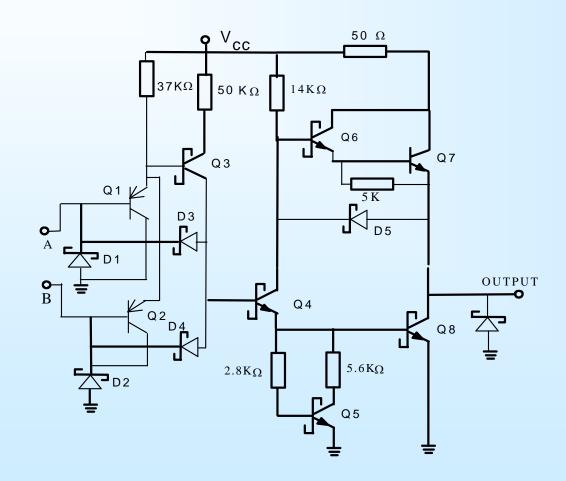

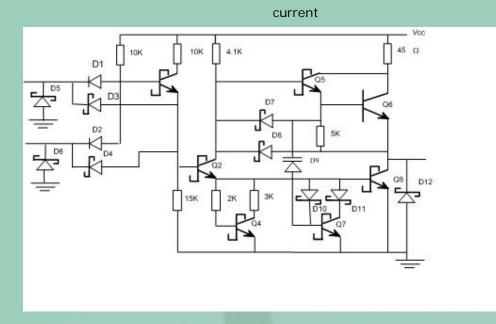

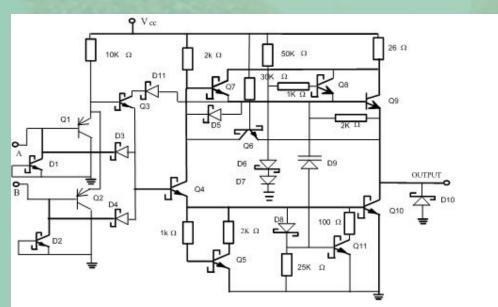

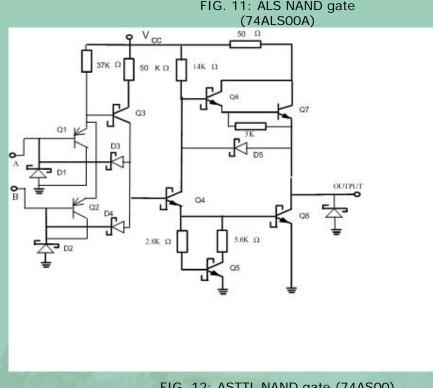

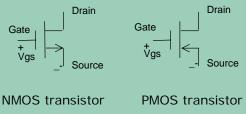

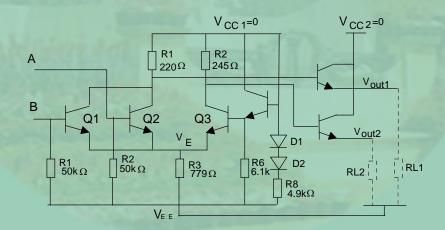

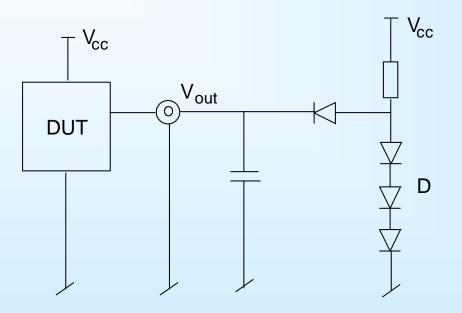

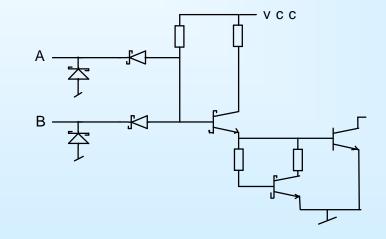

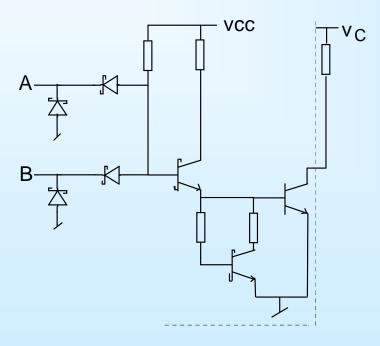

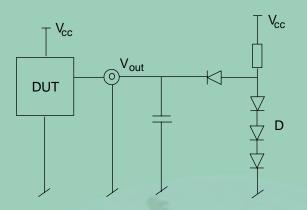

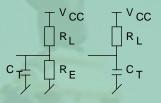

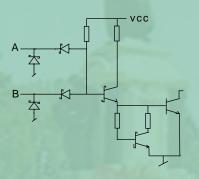

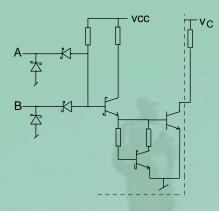

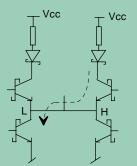

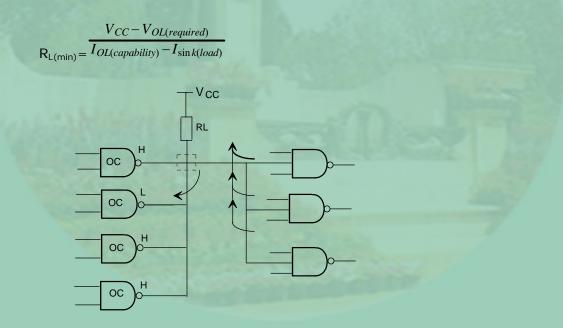

Logic families: Characteristics of logic families. TTL, CMOS, and ECL families.

#### Module 4: Combinational Functions (8)

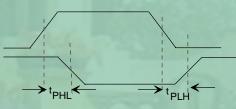

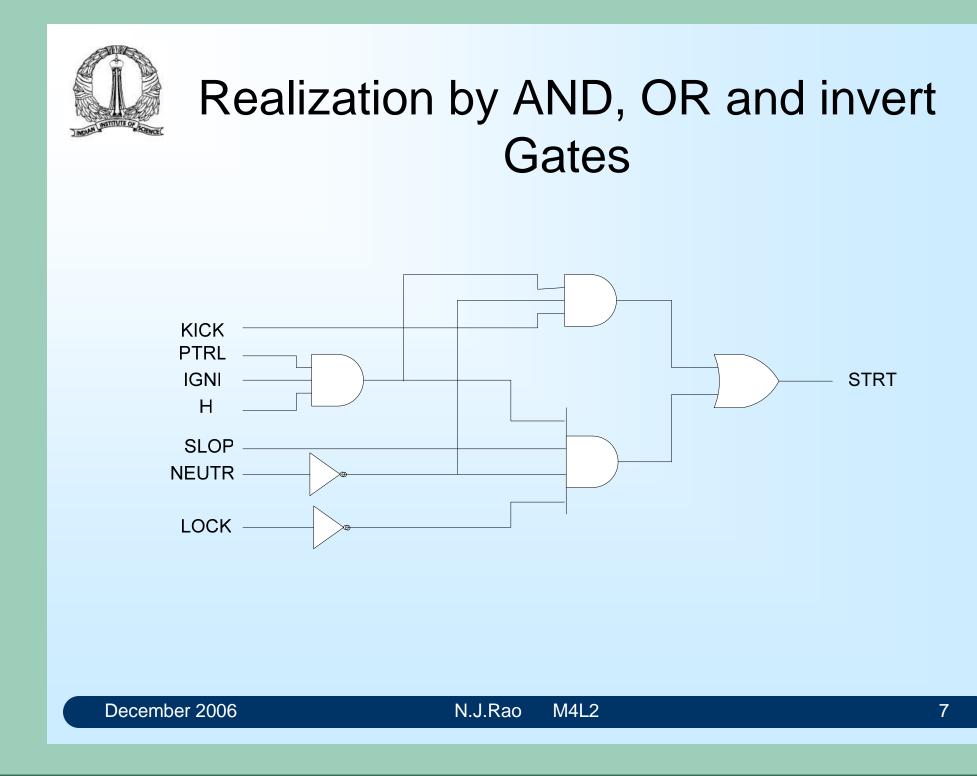

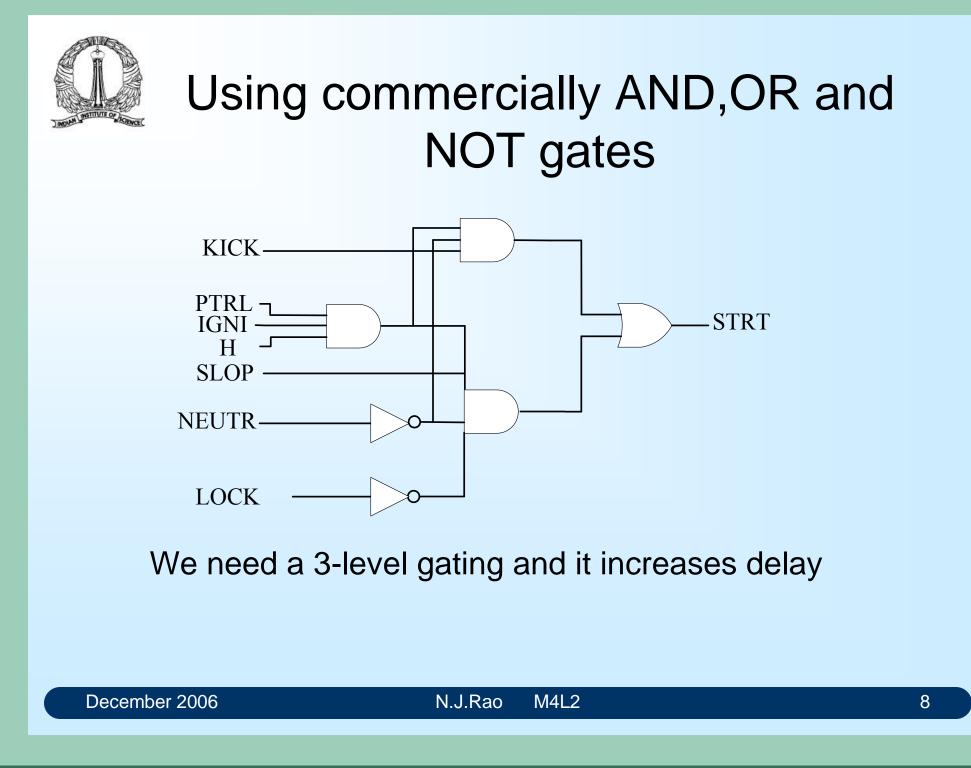

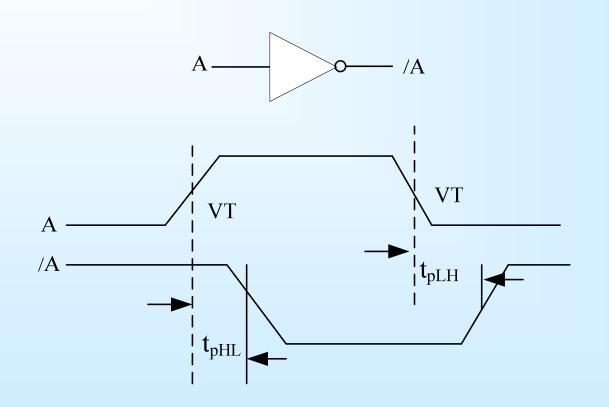

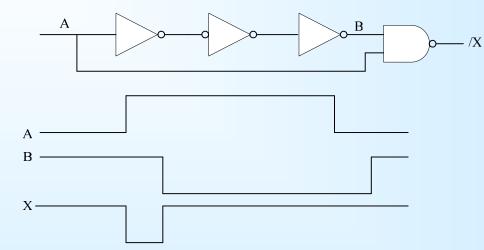

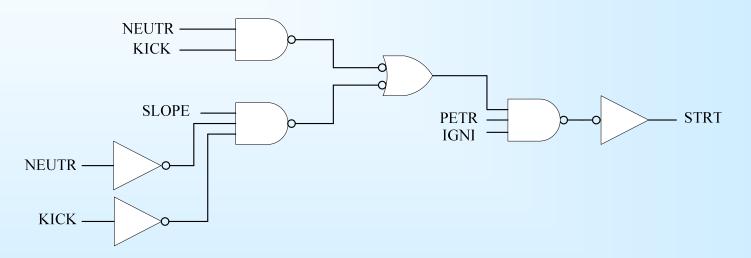

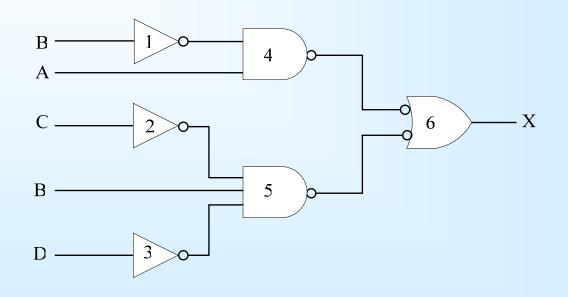

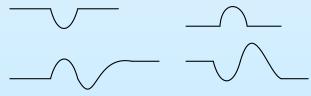

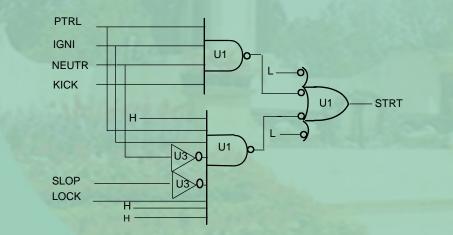

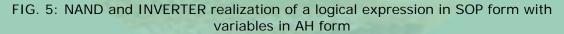

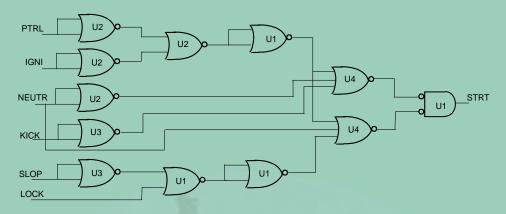

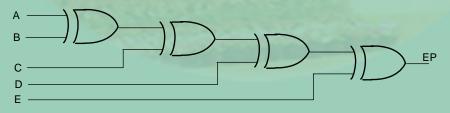

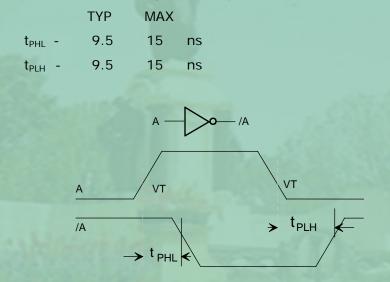

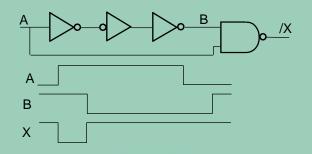

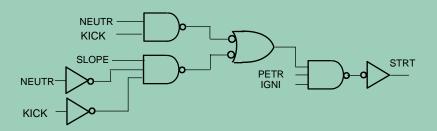

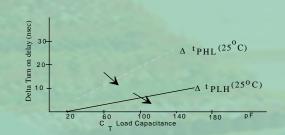

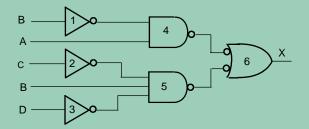

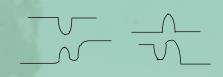

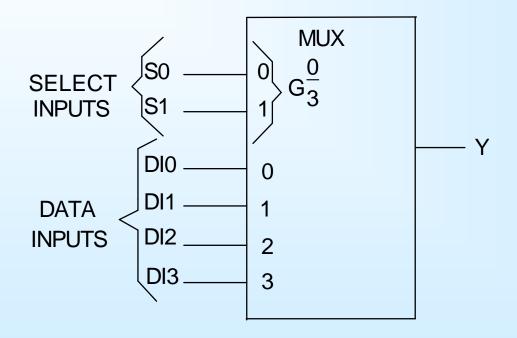

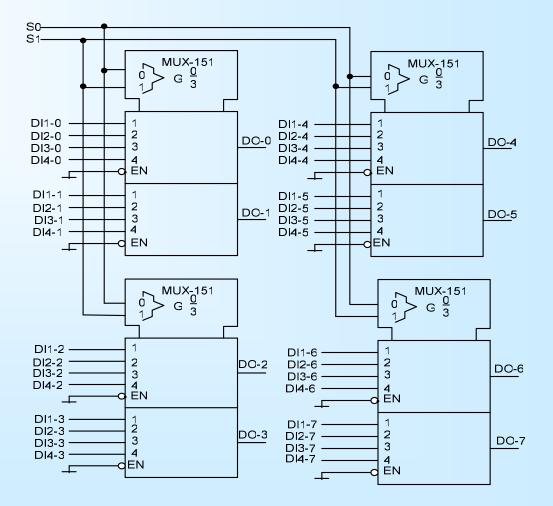

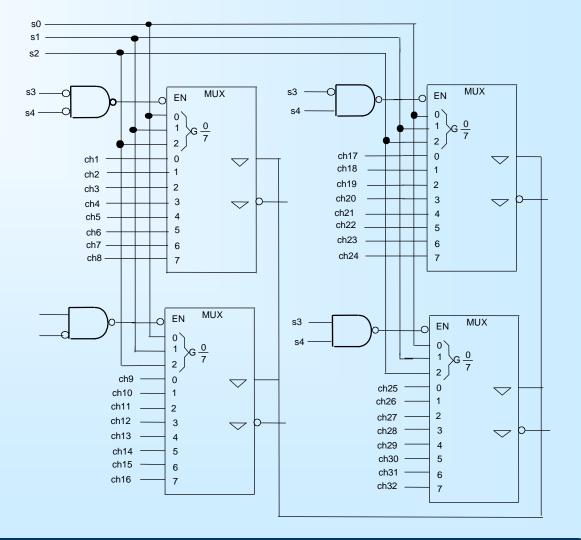

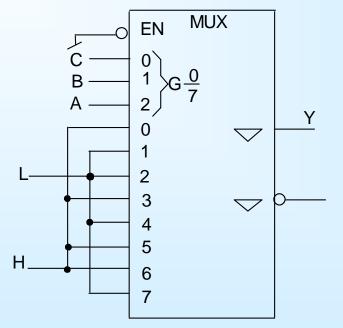

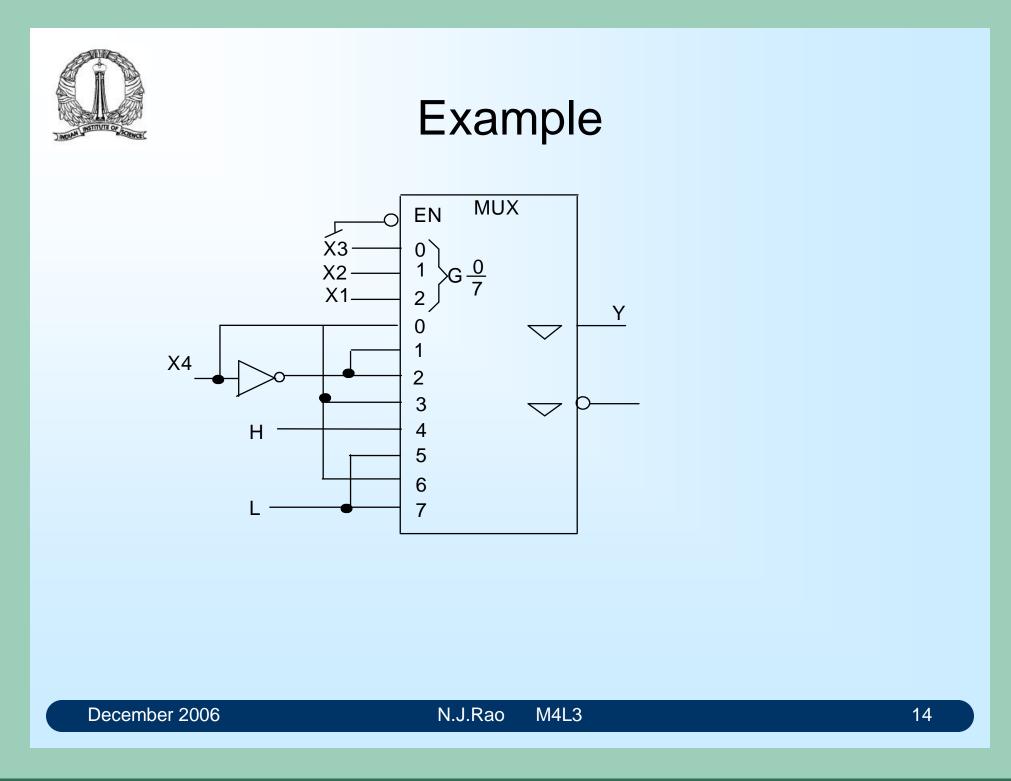

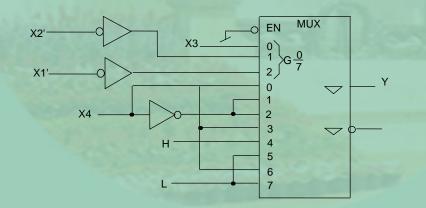

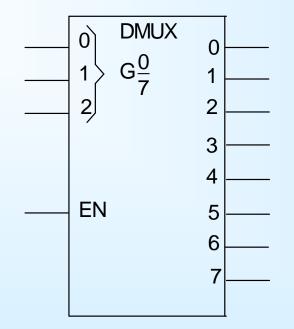

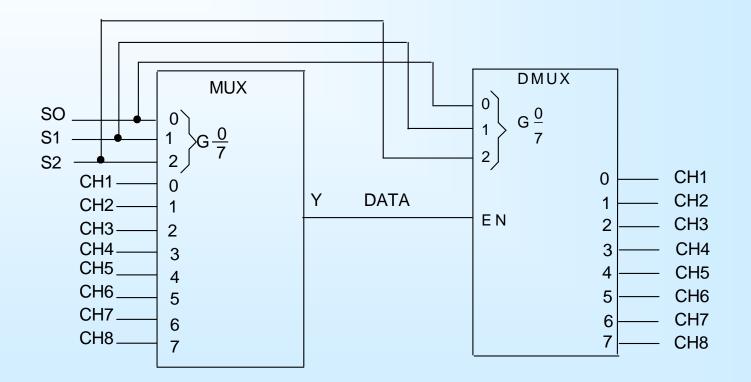

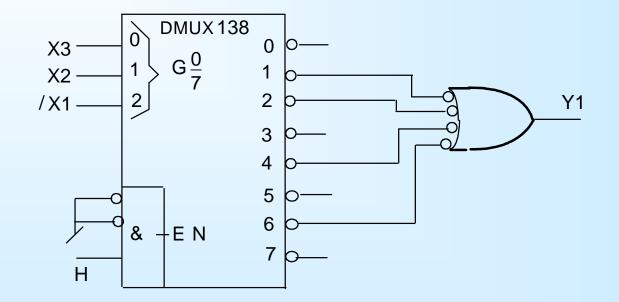

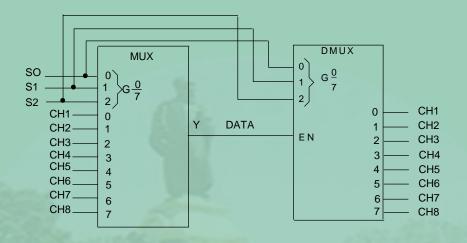

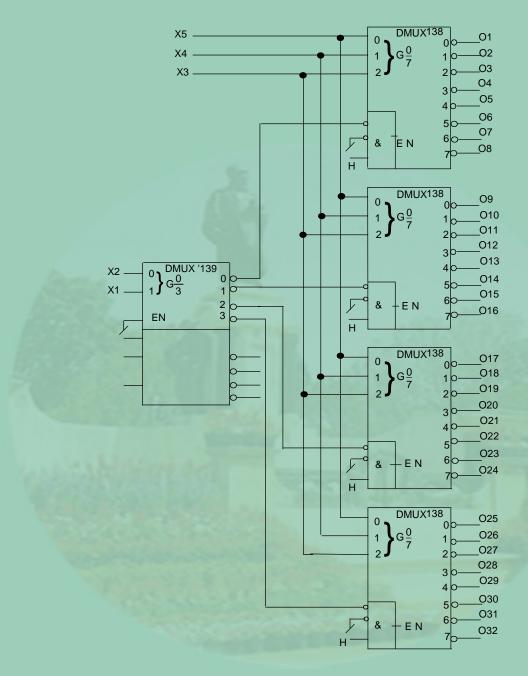

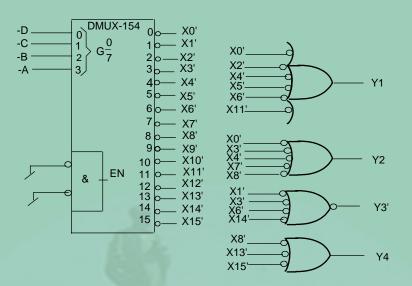

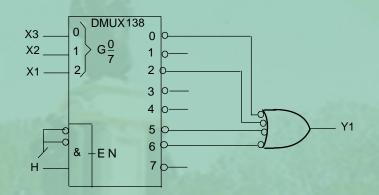

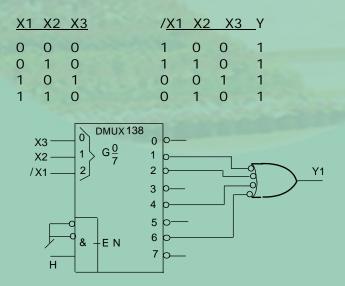

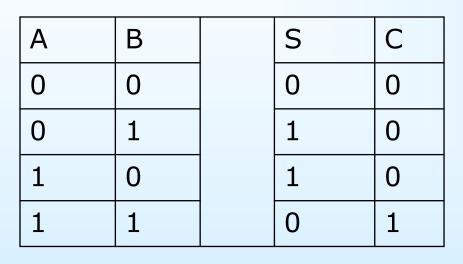

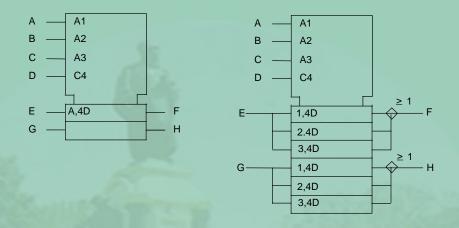

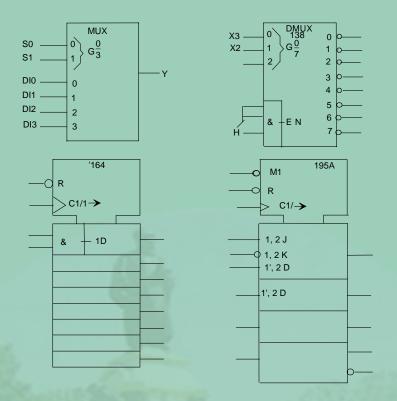

Realizing logical expressions using different logic gates and comparing their performance. Hardware aspects logic gates and combinational ICs: delays and hazards. Design of combinational circuits using combinational ICs: Combinational functions: code conversion, decoding, comparison, multiplexing, demultiplexing, addition, and subtraction.

#### Module 5: Analysis of Sequential Circuits (5)

Structure of sequential circuits: Moore and Melay machines. Flip-flops, excitation tables, conversions, practical clocking aspects concerning flip-flops, timing and triggering considerations. Analysis of sequential circuits: State tables, state diagrams and timing diagrams.

#### Module 6: Designing with Sequential MSIs (6)

Realization of sequential functions using sequential MSIs: counting, shifting, sequence generation, and sequence detection.

### Module 7: PLDs (3)

Programmable Logic Devices: Architecture and characteristics of PLDs,

### Module 8: Design of Digital Systems (6)

State diagrams and their features. Design flow: functional partitioning, timing relationships, state assignment, output racing. Examples of design of digital systems using PLDs

### Lecture Plan

| Modules                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Learning Units                                                                                                                            | Hours<br>per<br>topic | Total<br>Hours |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|----------------|

| 1. Number<br>Systems and<br>Codes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | <ol> <li>Binary, octal and hexadecimal number<br/>systems, and conversion of number with<br/>one radix to another</li> </ol>              | 1.5                   | 3              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2. Different binary codes                                                                                                                 | 1.5                   |                |

| 2. Logic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 3. Boolean algebra and Boolean operators                                                                                                  | 1.5                   |                |

| Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 4. Logic Functions                                                                                                                        | 1                     | _              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <ol> <li>Minimization of logic functions using<br/>Karnaugh -map</li> </ol>                                                               | 1.5                   | 5              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6. Quine-McClausky method of minimization of logic functions                                                                              | 1                     |                |

| 3.Logic Families                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 7. Introduction to Logic families                                                                                                         | 0.5                   |                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 8. TTL family                                                                                                                             | 1                     |                |

| Carrens                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 9. CMOS family                                                                                                                            | 1.5                   | 4              |

| And an and a second sec | 10. Electrical characteristics of logic families                                                                                          | 1                     |                |

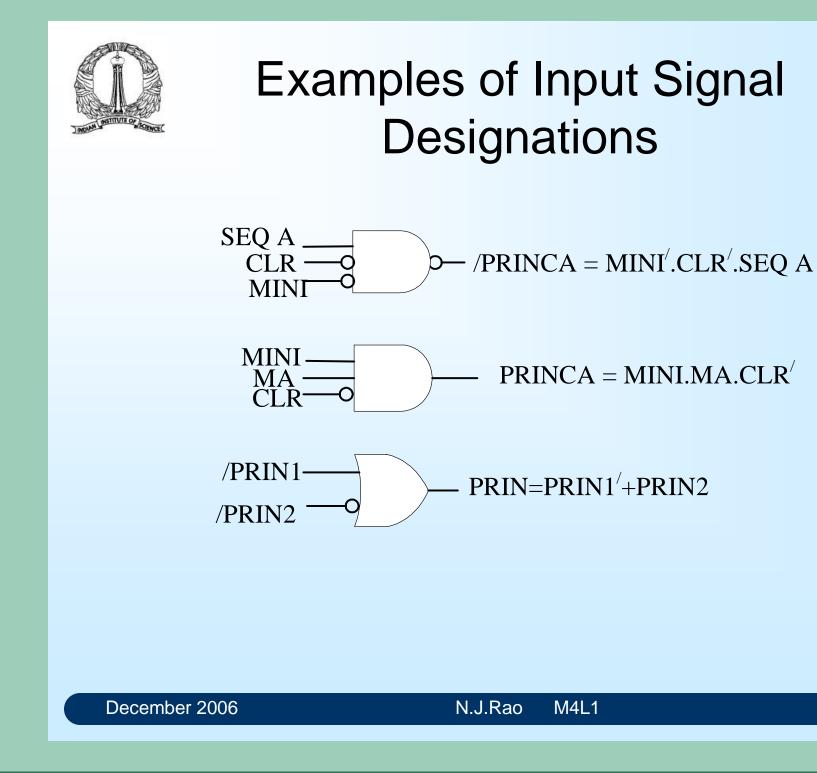

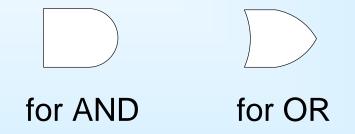

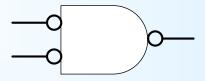

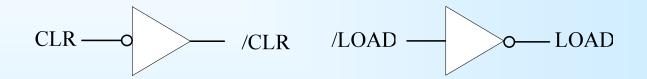

| 4. Combinational<br>Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 11. Introduction to combinational circuits, logic convention, and realization of simple combinational functions using gates               | 2                     |                |

| 1223022                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 12. Implications of delay and hazard                                                                                                      | 1                     | 8              |

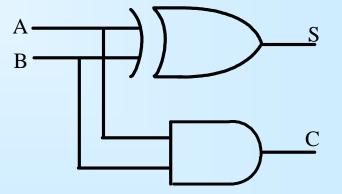

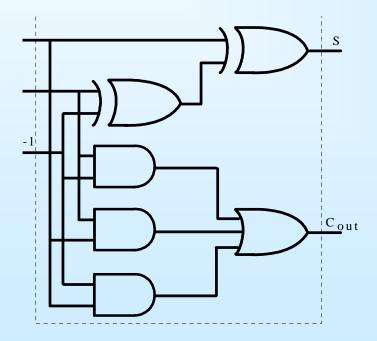

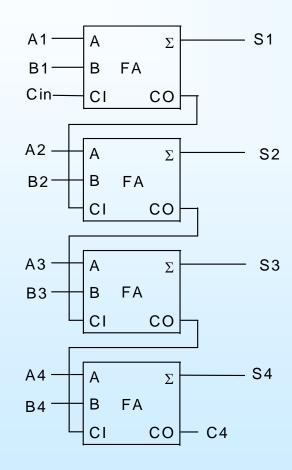

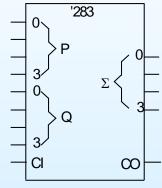

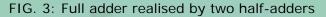

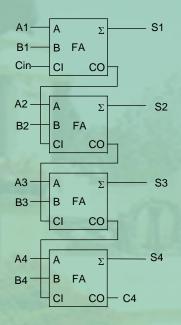

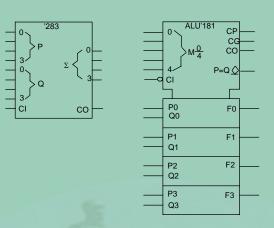

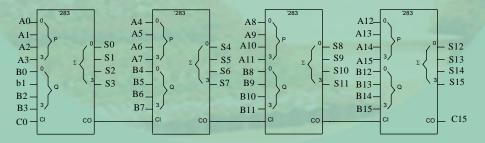

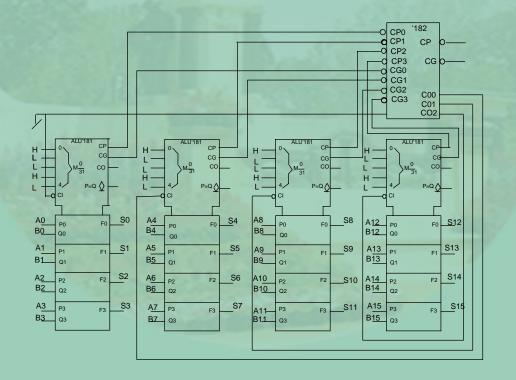

| Lease and the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 13. Realization of adders and subtractors                                                                                                 | 2                     |                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 14. Design of code converters, comparators, and decoders                                                                                  | 2                     |                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 15. Design of multiplexers, demultiplexers,                                                                                               | 1                     | 839            |

| 5. Analysis of Sequential                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 16. Introduction to sequential circuits: Moore and Mealy machines                                                                         | 1                     |                |

| Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <ol> <li>Introduction to flip-flops like SR, JK, D &amp; T<br/>with truth tables, logic diagrams, and<br/>timing relationships</li> </ol> | 1                     | 5              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 18. Conversion of Flip-Flops, Excitation table                                                                                            | 1                     |                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 19. State tables, and realization of state stables                                                                                        | 2                     |                |

| 6. Design with                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 20. Design of shift registers and counters                                                                                                | 2                     |                |

| Sequential MSIs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 21. Design of counters                                                                                                                    | 2                     | 6              |

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 22. Design of sequence generators and detectors                                                                                           | 2                     |                |

| 7. PLDs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 23. Introduction to Programmable Devices                                                                                                  | 1                     |                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 24. Architecture of PLDs                                                                                                                  | 2                     | 3              |

| 8. Design of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 25. State diagrams and their features                                                                                                     | 2                     |                |

| Digital Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 26. Design flow                                                                                                                           | 1                     | 6              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 27. Design of digital systems using PLDs                                                                                                  | 3                     |                |

#### Learning Objectives of the Course

#### 1. Recall

- 1.1 List different criteria that could be used for optimization of a digital circuit.

- **1.2** List and describe different problems of digital circuits introduced by the hardware limitations.

#### 2. Comprehension

- 2.1 Describe the significance of different criteria for design of digital circuits.

- 2.2 Describe the significance of different hardware related problems encountered in digital circuits.

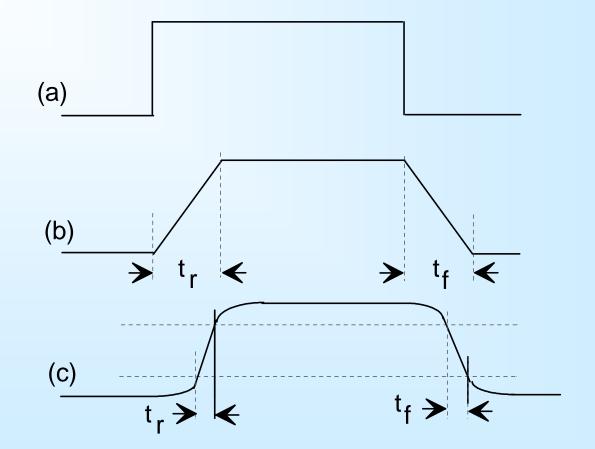

- 2.3 Draw the timing diagrams for identified signals in a digital circuit.

#### 3. Application

- 3.1 Determine the output and performance of given combinational and sequential circuits.

- 3.2 Determine the performance of a given digital circuit with regard to an identified optimization criterion.

#### 4. Analysis

- 4.1 Compare the performances of combinational and sequential circuits implemented with SSIs/MSIs and PLDs.

- 4.2 Determine the function and performance of a given digital circuit.

- 4.3 Identify the faults in a given circuit and determine the consequences of the same on the circuit performance.

- 4.4 Draw conclusions on the behavior of a given digital circuit with regard to hazards, asynchronous inputs, and output races.

- 4.5 Determine the appropriateness of the choice of the ICs used in a given digital circuit.

- 4.6 Determine the transition sequence of a given state in a state diagram for a given input sequence.

### 5. Synthesis

- 5.1 Generate multiple digital solutions to a verbally described problem.

- 5.2 Modify a given digital circuit to change its performance as per specifications.

#### 6. Evaluation

- 6.1 Evaluate the performance of a given digital circuit.

- 6.2 Assess the performance of a given digital circuit with Moore and Melay configurations.

- 6.3 Compare the performance of given digital circuits with respect to their speed, power consumption, number of ICs, and cost.

#### **Digital Systems: Motivation**

A digital circuit is one that is built with devices with two well-defined states. Such circuits can process information represented in binary form. Systems based on digital circuits touch all aspects our present day lives. The present day home products including electronic games and appliances, communication and office automation products, computers with a wide range of capabilities, and industrial instrumentation and control systems, electro-medical equipment, and defence and aerospace systems are heavily dependent on digital circuits. Many fields that emerged later to digital electronics have peaked and levelled off, but the application of digital concepts appears to be still growing exponentially. This unprecedented growth is powered by the semiconductor technology, which enables the introduction of more and complex integrated circuits. The complexity of an integrated circuit is measured in terms of the number of transistors that can be integrated into a single unit. The number of transistors in a single integrated circuit has been doubling every eighteen months (Moore' Law) for several decades and reached the figure of almost one billion transistors per chip. This allowed the circuit designers to provide more and more complex functions in a single unit.

The introduction of programmable integrated circuits in the form of microprocessors in 70s completely transformed every facet of electronics. While fixed function integrated circuits and microprocessors coexisted for considerable time, the need to make the equipment smaller and portable lead to replacement of fixed function devices with programmable devices. With the all pervasive presence of the microprocessor and the increasing usage of other programmable circuits like PLDs (Programmable Logic devices), FPGAs (Field Programmable Gate Arrays) and ASICs (Application Specific Integrated Circuits), the very nature of digital systems is continuously changing.

The central role of digital circuits in all our professional and personal lives makes it imperative that every electrical and electronics engineer acquire good knowledge of relevant basic concepts and ability to work with digital circuits.

At present many of the undergraduate programmes offer two to four courses in the area of digital systems, with at least two of them being core courses. The course under consideration constitutes the first course in the area of digital systems. The rate of obsolescence of knowledge, design methods, and design tools is uncomfortably high. Even the first level course in digital electronics is not exempt from this obsolescence.

Any course in electronics should enable the students to design circuits to meet some stated requirements as encountered in real life situations. However, the design approaches should be based on a sound understanding of the underlying principles. The basic feature of all design problems is that all of them admit multiple solutions. The selection of the final solution depends on a variety of criteria that could include the size and cost of the substrate on which the components are assembled, the cost of components, manufacturability,

reliability, speed etc.

The course contents are designed to enable the students to design digital circuits of medium level of complexity taking the functional and hardware aspects in an integrated manner within the context of commercial and manufacturing constraints. However, no compromises are made with regard to theoretical aspects of the subject.

### Learning Objectives

### Module 1: Number Systems and Codes (3)

Number systems: Binary, octal, and hexa-decimal number systems, binary arithmetic. Codes: Binary code, excess-3 code, gray code, error detection and correction codes.

### Recall

- 1. Describe the format of numbers of different radices?

- 2. What is parity of a given number?

### Comprehension

- 1. Explain how a number with one radix is converted into a number with another radix.

- 2. Summarize the advantages of using different number systems.

- 3. Interpret the arithmetic operations of binary numbers.

- 4. Explain the usefulness of different coding schemes.

- 5. Explain how errors are detected and/or corrected using different codes.

### Application

- 1. Convert a given number from one system to an equivalent number in another system.

- 2. Illustrate the construction of a weighted code.

Analysis: Nil

Synthesis: Nil

**Evaluation: Nil**

# Digital Electronics Module 1: Number Systems and Codes - Number Systems N.J. Rao Indian Institute of Science

### Numbers

We use numbers

- to communicate

- to perform tasks

- to quantify

- to measure

- Numbers have become symbols of the present era

- Many consider what is not expressible in terms of numbers is not worth knowing

### Number Systems in use

Symbolic number system

- uses Roman numerals (I = 1, V = 5, X = 10, L = 50, C = 100, D = 500 and M = 1000)

- still used in some watches

Weighted position system

- Decimal system is the most commonly used

- Decimal numbers are based on Indian numerals

- Radix used is 10

## Other weighted position systems

- Advent of electronic devices with two states created a possibility of working with binary numbers

- Binary numbers are most extensively used

- Binary system uses radix 2

- Octal system uses radix 8

- Hexa-decimal system uses radix 16

# Weighted Position Number System

- Value associated with a digit is dependent on its position

- The value of a number is weighted sum of its digits  $2357 = 2 \times 10^3 + 3 \times 10^2 + 5 \times 10^1 + 7 \times 10^0$

- Decimal point allows negative and positive powers of 10

526.47 = 5 x 10<sup>2</sup> +2 x 10<sup>1</sup> + 6 x 10<sup>0</sup> + 4 x 10<sup>-1</sup> + 7 x 10<sup>-2</sup>

- 10 is called the *base* or *radix* of the number system

## General positional number system

- Any integer > 2 can serve as the radix

- Digit position 'i' has weight r<sup>i</sup>.

- The general form of a number is

$d_{p-1} d_{p-2}, \dots d_1, d_0 \cdot d_{-1} d_{-2} \dots d_{-n}$

*p* digits to the left of the point (*radix point*) and *n* digits to the right of the point

# General positional number system (2)

• The value of the number is

$$\mathsf{D} = \sum_{i=-n}^{p-1} d_i r^{i}$$

- Leading and trailing zeros have no values

- The values d<sub>i</sub>s can take are limited by the radix value

- A number like (357)<sub>5</sub> is incorrect

## **Binary Number System**

- Uses 2 as its radix

- Has only two numerals, 0 and 1

Example:

$(N)_2 = (11100110)_2$

- It is an eight digit binary number

- The binary digits are also known as bits

- (N)<sub>2</sub> is an 8-bit number

### Binary numbers to Decimal Number

$(N)_{2} = (11100110)_{2}$ Its decimal value is given by,  $(N)_{2} = 1 \times 2^{7} + 1 \times 2^{6} + 1 \times 2^{5} + 0 \times 2^{4} + 0 \times 2^{3}$  $+ 1 \times 2^{2} + 1 \times 2^{1} + 0 \times 2^{0}$  $= 128 + 64 + 32 + 0 + 0 + 4 + 2 + 0 = (230)_{10}$

# Binary fractional number to Decimal number

- A binary fractional number  $(N)_2 = 101.101$

- Its decimal value is given by

N)2 = 1 x 2<sup>2</sup> + 0 x 2<sup>1</sup> + 1 x 2<sup>0</sup>

+ 1 x 2<sup>-1</sup> + 0 x 2<sup>-2</sup> + 1 x 2<sup>-3</sup>

= 4 + 0 + 1 +

$$\frac{1}{2}$$

+ 0 +  $\frac{1}{8}$

= 5 + 0.5 + 0.125 = (5.625)<sub>10</sub>

December 2006

## Some features of Binary Numbers

- Require very long strings of 1s and 0s

- Some simplification can be done through grouping

- 3-bit groupings: Octal (radix 8) groups three binary digits Digits will have one of the eight values 0, 1, 2, 3, 4, 5, 6 and 7

- 4-digit groupings: Hexa-decimal (radix 16)

Digits will have one of the sixteen values 0 through 15.

Decimal values from 10 to 15 are designated as A (=10), B (=11), C (=12), D (=13), E (=14) and F (=15)

### Conversion of binary numbers

Conversion to an octal number

- Group the binary digits into groups of three

- $-(11011001)_2 = (011)(011)(001) = (331)_8$

- Conversion to an hexa-decimal number

- Group the binary digits into groups of four

- $(11011001)_2 = (1101)(1001) = (D9)_{16}$

# Changing the radix of numbers

- Conversion requires, sometimes, arithmetic operations

- The decimal equivalent value of a number in any radix

$$\mathsf{D} = \sum_{i=-n}^{p-1} d_i r^i$$

### Examples

$$(331)_8 = 3 \times 8^2 + 3 \times 8^1 + 1 \times 8^0 = 192 + 24 + 1 = (217)_{10}$$

$$(D9)_{16} = 13 \times 16^1 + 9 \times 16^0 = 208 + 9 = (217)_{10}$$

$$(33.56)_8 = 3 \times 8^1 + 3 \times 8^0 + 5 \times 8^{-1} + 6 \times 8^{-2} = (27.69875)_{10}$$

$$(E5.A)_{16} = 14 \times 16^1 + 5 \times 16^0 + 10 \times 16^{-1} = (304.625)_{10}$$

December 2006

Conversion of decimal numbers to numbers with radix r

Represent a number with radix r as

$D = ((\dots ((d_{n-1}).r + d_{n-2}) r + \dots).r + d_1).r + d_0$

To convert a number with radix r to a decimal number

- Divide the right hand side by r

- Remainder: d<sub>0</sub>

- Quotient:  $Q = ((... ((d_{n-1}).r + d_{n-2}) r + ...).r + d_1)$

- Division of Q by r gives d<sub>1</sub> as the remainder

- so on

## **Example of Conversion**

|                             | Quotient | Remainder |  |

|-----------------------------|----------|-----------|--|

| 156 ÷ 2                     | 78       | 0         |  |

| 78 ÷ 2                      | 39       | 0         |  |

| 39 ÷ 2                      | 19       | 1         |  |

| 19 ÷ 2                      | 9        | 1         |  |

| 9 ÷ 2                       | 4        | 1         |  |

| 4 ÷ 2                       | 2        | 0         |  |

| 2 ÷ 2                       | 1        | 0         |  |

| 1 ÷ 2                       | 0        | 1         |  |

| $(156)_{10} = (10011100)_2$ |          |           |  |

December 2006

## **Example of Conversion**

|                           | Quotient | Remainder |  |  |

|---------------------------|----------|-----------|--|--|

| 678 ÷ 8                   | 84       | 6         |  |  |

| 84 ÷ 8                    | 10       | 4         |  |  |

| 10 ÷ 8                    | 1        | 2         |  |  |

| 1 ÷ 8                     | 0        | 1         |  |  |

| $(678)_{10} = (1246)_8$   |          |           |  |  |

|                           | Quotient | Remainder |  |  |

| 678 ÷ 16                  | 42       | 6         |  |  |

| 42 ÷ 16                   | 2        | A         |  |  |

| 2 ÷ 16                    | 0        | 2         |  |  |

| $(678)_{10} = (2A6)_{16}$ |          |           |  |  |

December 2006

## **Negative Numbers**

Sign-Magnitude representation

- "+" sign before a number indicates it as a positive number

- "-" sign before a number indicates it as a negative number

- Not very convenient on computers

- Replace "+" sign by "0" and "-" by "1"

$(+1100101)_2 \rightarrow (01100101)_2$  $(+101.001)_2 \rightarrow (0101.001)_2$  $(-10010)_2 \rightarrow (110010)_2$  $(-110.101)_2 --. (1110.101)_2$

December 2006

# Representing signed numbers

- Diminished Radix Complement (DRC) or (r-1) - complement

- Radix Complement (RXC) or r-complement Binary numbers

- DRC is known as "one's-complement"

- RXC is known as "two's-complement" Decimal numbers

- DRC is known as 9's-complement

- RXC is known as 10's-complement

# One's Complement Representation

The most significant bit (MSD) represents the sign If MSD is a "0"

- The number is positive

- Remaining (n-1) bits directly indicate the magnitude

If the MSD is "1"

- The number is negative

- Complement of all the remaining (n-1) bits gives the magnitude

# Example: One's complement

### $1111001 \rightarrow (1)(111001)$

- First (sign) bit is 1: The number is negative

- Ones' Complement of  $111001 \rightarrow 000110$  $\rightarrow (6)_{10}$

### Range of n-bit numbers

One's complement numbers:

| 0111111 | + 63 |      |

|---------|------|------|

| 0000110 | >    | + 6  |

| 0000000 | >    | + 0  |

| 1111111 | >    | + 0  |

| 1111001 | >    | - 6  |

| 1000000 | >    | - 63 |

- "0" is represented by 000....0 and 111....1

- 7- bit number covers the range from +63 to -63.